Visual circuit tutorial: Difference between revisions

(WIP - just so that I don't lose edits so far by accident) |

(Ditto) |

||

| Line 4: | Line 4: | ||

the diagrams at a basic level in simple language, omitting details that are | the diagrams at a basic level in simple language, omitting details that are | ||

unimportant when starting out. | unimportant when starting out. | ||

You might want to read [http://visual6502.org/wiki/index.php?title=JssimUserHelp the Visual 6502 user's guide] and the [[Visual 2C02]] page first. | |||

== What the different colored areas are == | == What the different colored areas are == | ||

| Line 29: | Line 31: | ||

When a piece of polysilicon is sandwiched between two areas of diffusion, it | When a piece of polysilicon is sandwiched between two areas of diffusion, it | ||

acts as a gate, only letting current through when the polysilicon is powered | acts as a gate, only letting current through when the polysilicon is powered | ||

(or, equivalently, | (or, equivalently, ''high'', ''1'', or ''open''). The diffusion area from which | ||

current will flow when the gate is open is called the | current will flow when the gate is open is called the ''source''. The diffusion | ||

area into which current will flow is called the | area into which current will flow is called the ''drain''. The gate together with | ||

the source and drain is what makes a transistor. | the source and drain is what makes a transistor. | ||

| Line 49: | Line 51: | ||

== Nodes == | == Nodes == | ||

Electrically common areas are called | Electrically common areas are called ''nodes'' in Visual 6502/2C02/2A03. Clicking | ||

on a node will highlight it, making it easier to see how things are connected | on a node will highlight it, making it easier to see how things are connected | ||

(clicking on powered or grounded diffusion won't work; these only modify | (clicking on powered or grounded diffusion won't work; these only modify | ||

| Line 57: | Line 59: | ||

nodenames.js. | nodenames.js. | ||

The | The '''Find:''' edit field can be used to locate nodes, either by numeric ID or by | ||

name. | name. | ||

| Line 72: | Line 74: | ||

output wire is hence the inverse of the input wire. | output wire is hence the inverse of the input wire. | ||

When one node is the inverse of another, it is said that it | When one node is the inverse of another, it is said that it ''inverts into'' the | ||

other node. | other node. | ||

| Line 87: | Line 89: | ||

the values on the gates in the red circles. | the values on the gates in the red circles. | ||

The gate in the blue circle is part of a | The gate in the blue circle is part of a ''pass transistor'', so called because | ||

it passes current between two nodes rather than driving or grounding a node. | it passes current between two nodes rather than driving or grounding a node. | ||

The gate in this case is apu_clk1, and we say that value is "buffered on | The gate in this case is '''apu_clk1''', and we say that value is "buffered on | ||

apu_clk1". | '''apu_clk1'''". | ||

== Storage elements == | == Storage elements == | ||

| Line 101: | Line 103: | ||

bus line). | bus line). | ||

Below is the VBlank flag from Visual 2C02. To the left the vbl_flag node is | Below is the VBlank flag from Visual 2C02. To the left the '''vbl_flag''' node is | ||

highlighted, and to the right its inverse is highlighted. (We would label the | highlighted, and to the right its inverse is highlighted. (We would label the | ||

inverse | inverse '''/vbl_flag''', where "/" denotes "inverse" or "active low"). As can be | ||

seen by the two gates in white circles, each inverts into the other, forming | seen by the two gates in white circles, each inverts into the other, forming | ||

two cross-coupled inverters. | two cross-coupled inverters. | ||

| Line 109: | Line 111: | ||

[[File:vis_crossreg.png|none]] | [[File:vis_crossreg.png|none]] | ||

(The different highlight colors are due to vbl_flag being set when the | (The different highlight colors are due to '''vbl_flag''' being set when the | ||

screenshot was taken.) | screenshot was taken.) | ||

The two gates in blue circles set and clear the latch, respectively. To clear | The two gates in blue circles set and clear the latch, respectively. To clear | ||

the latch, vbl_flag is driven low. To set the latch, /vbl_flag is driven low. | the latch, '''vbl_flag''' is driven low. To set the latch, '''/vbl_flag''' is driven low. | ||

=== Clocked latches === | === Clocked latches === | ||

| Line 119: | Line 121: | ||

When a latch can be set directly from the value of some line, e.g. a data bus | When a latch can be set directly from the value of some line, e.g. a data bus | ||

line, an arrangement involving a clock is often used. The motivation is to | line, an arrangement involving a clock is often used. The motivation is to | ||

avoid having to form both data_line and /data_line and route them to the | avoid having to form both '''data_line''' and '''/data_line''' and route them to the | ||

respective terminals of the latch, which would use more logic. (The clock is | respective terminals of the latch, which would use more logic. (The clock is | ||

already routed all around the chip, so mixing it in usually isn't as much of a | already routed all around the chip, so mixing it in usually isn't as much of a | ||

problem.) | problem.) | ||

As an example, here's the noi_lfsrmode node (the "Loop noise" flag from | As an example, here's the '''noi_lfsrmode''' node (the "Loop noise" flag from | ||

[[$400E]]): | [[APU Noise|$400E]]): | ||

[[File:vis_clockedreg.png|none]] | [[File:vis_clockedreg.png|none]] | ||

When apu_clk1 is high, noi_lfsrmode will flow into the second highlighted node, | When '''apu_clk1''' is high, '''noi_lfsrmode''' will flow into the second highlighted node, | ||

which then inverts into /noi_lfsrmode, forming a cross-coupled inverter latch. | which then inverts into '''/noi_lfsrmode''', forming a cross-coupled inverter latch. | ||

While apu_clk1 is low, the loop will be broken momentarily, and during this | While '''apu_clk1''' is low, the loop will be broken momentarily, and during this | ||

phase a new value can be copied into the latch by opening the w400e gate (which | phase a new value can be copied into the latch by opening the '''w400e''' gate (which | ||

goes high on writes to $400E). If the loop was not broken during the write | goes high on writes to $400E). If the loop was not broken during the write | ||

operation, the old value in the latch would interfere with setting a new value. | operation, the old value in the latch would interfere with setting a new value. | ||

| Line 141: | Line 143: | ||

nor ground, it will retain its value for a while through capacitance. This is | nor ground, it will retain its value for a while through capacitance. This is | ||

used to store some short-lived data "on the wire" without requiring a latch | used to store some short-lived data "on the wire" without requiring a latch | ||

(this is called [http://en.wikipedia.org/wiki/Dynamic_logic_%28digital_electronics%29 dynamic logic], since it has time-dependent behavior beyond | (this is called [http://en.wikipedia.org/wiki/Dynamic_logic_%28digital_electronics%29 dynamic logic], | ||

just the input clock). As an example, here's the read buffer for the VBL flag, | since it has time-dependent behavior beyond just the input clock). As an example, | ||

which lets its value be read even though reading $2002 immediately clears the | here's the read buffer for the VBL flag, which lets its value be read even though | ||

VBL flag: | reading [[PPU_registers|$2002]] immediately clears the VBL flag: | ||

[[File:vis_vblbuf.png|none]] | [[File:vis_vblbuf.png|none]] | ||

When the circled gate (/read_2002_output_vblank_flag) goes low, the gate | When the circled gate ('''/read_2002_output_vblank_flag''') goes low, the gate | ||

closes, holding the value. When the circled gate is high, the value of vbl_flag | closes, holding the value. When the circled gate is high, the value of '''vbl_flag''' | ||

(or rather /vbl_flag in this case) is connected to the wire. | (or rather '''/vbl_flag''' in this case) is connected to the wire. | ||

== Terms == | == Terms == | ||

Revision as of 17:58, 24 May 2013

This is a crash course on making sense of the circuit displays in Visual 6502/2C02/2A03, written for people without much low-level electronics experience (like the author). It aims to present the information needed to read the diagrams at a basic level in simple language, omitting details that are unimportant when starting out.

You might want to read the Visual 6502 user's guide and the Visual 2C02 page first.

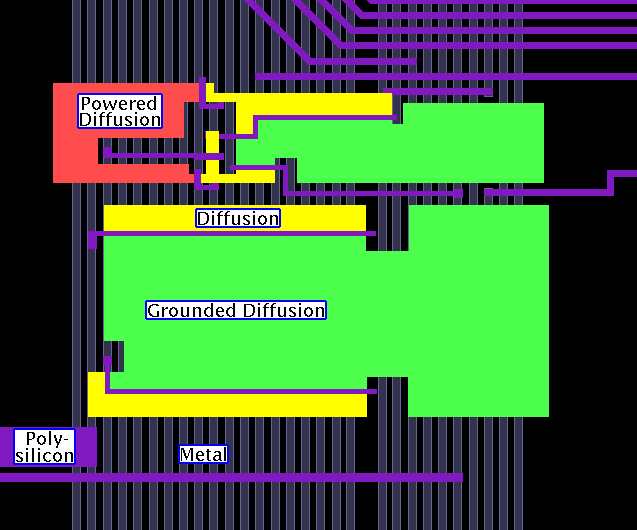

What the different colored areas are

Let's start by defining what the different colors mean:

* Green areas are diffusion (explained below) connected to ground. * Red areas are diffusion connected to VCC (power). * Yellow areas are diffusion that is neither connected directly to ground nor directly to VCC. * Gray areas are metal. * Purple areas are polysilicon.

At the level presented here, diffusion, metal, and polysilicon can be thought of as equivalent when viewed in isolation; they all conduct current. The important difference is in how they interact with each other, which is explained below.

Building blocks

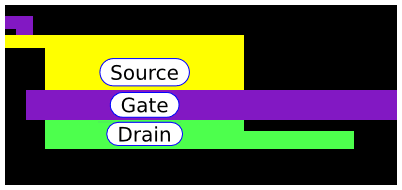

Transistors

When a piece of polysilicon is sandwiched between two areas of diffusion, it acts as a gate, only letting current through when the polysilicon is powered (or, equivalently, high, 1, or open). The diffusion area from which current will flow when the gate is open is called the source. The diffusion area into which current will flow is called the drain. The gate together with the source and drain is what makes a transistor.

Power sources

Around an area of powered diffusion we will often see something like the following (note the distinctive "hook" in the polysilicon):

Here the polysilicon acts roughly like a resistor, preventing a short from VCC to ground when the power source would otherwise have a direct connection to ground along some path of open gates.

Nodes

Electrically common areas are called nodes in Visual 6502/2C02/2A03. Clicking on a node will highlight it, making it easier to see how things are connected (clicking on powered or grounded diffusion won't work; these only modify properties of other nodes and are not nodes themselves). When a node is highlighted, a numeric ID unique to the node will be displayed in the upper right, along with a name for the node if it has one. Node names are defined in nodenames.js.

The Find: edit field can be used to locate nodes, either by numeric ID or by name.

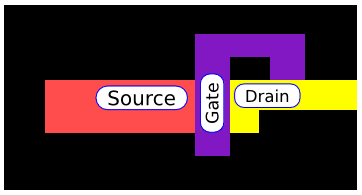

Logic elements

Inverters

An inverter is constructed like in the image below:

When the input gate is low, current flows into the output wire. When the input gate is high, current flows into ground, driving the output wire low. The output wire is hence the inverse of the input wire.

When one node is the inverse of another, it is said that it inverts into the other node.

NOR gates

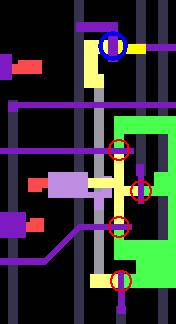

Below is an example of a NOR gate taken from Visual 2A03, related to controlling when the first square channel is silenced:

If any of the gates in red circles are open (high), the current from the highlighted node will go to ground instead of to the gate in the blue circle on the top. Hence the value that reaches the gate in the blue circle is the NOR of the values on the gates in the red circles.

The gate in the blue circle is part of a pass transistor, so called because it passes current between two nodes rather than driving or grounding a node. The gate in this case is apu_clk1, and we say that value is "buffered on apu_clk1".

Storage elements

Cross-coupled inverters

Two cross-coupled inverters will make a latch (an element that stores a single bit). This arrangement is often used for latches that are set or cleared by specific logic rather than by having a value copied into them (from e.g. a data bus line).

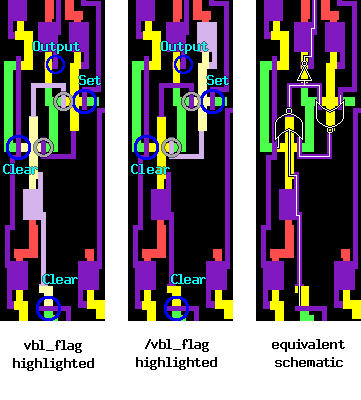

Below is the VBlank flag from Visual 2C02. To the left the vbl_flag node is highlighted, and to the right its inverse is highlighted. (We would label the inverse /vbl_flag, where "/" denotes "inverse" or "active low"). As can be seen by the two gates in white circles, each inverts into the other, forming two cross-coupled inverters.

(The different highlight colors are due to vbl_flag being set when the screenshot was taken.)

The two gates in blue circles set and clear the latch, respectively. To clear the latch, vbl_flag is driven low. To set the latch, /vbl_flag is driven low.

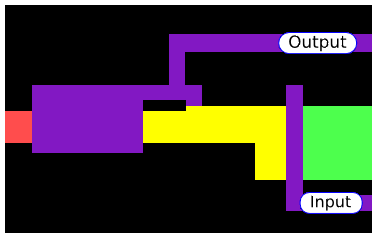

Clocked latches

When a latch can be set directly from the value of some line, e.g. a data bus line, an arrangement involving a clock is often used. The motivation is to avoid having to form both data_line and /data_line and route them to the respective terminals of the latch, which would use more logic. (The clock is already routed all around the chip, so mixing it in usually isn't as much of a problem.)

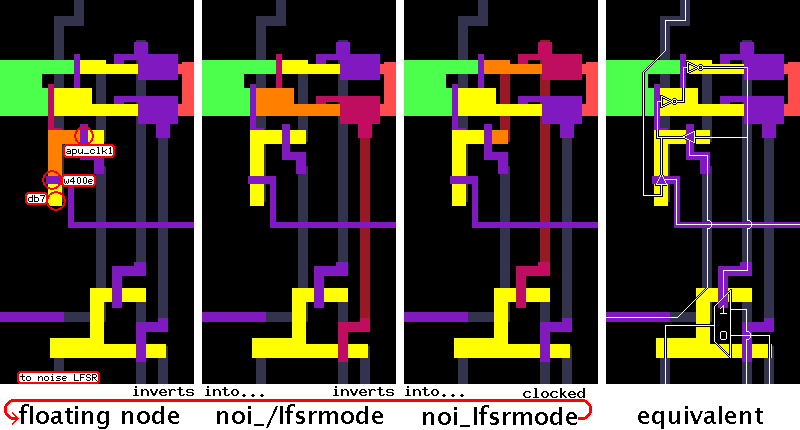

As an example, here's the noi_lfsrmode node (the "Loop noise" flag from $400E):

When apu_clk1 is high, noi_lfsrmode will flow into the second highlighted node, which then inverts into /noi_lfsrmode, forming a cross-coupled inverter latch. While apu_clk1 is low, the loop will be broken momentarily, and during this phase a new value can be copied into the latch by opening the w400e gate (which goes high on writes to $400E). If the loop was not broken during the write operation, the old value in the latch would interfere with setting a new value.

Wire capacitance as storage

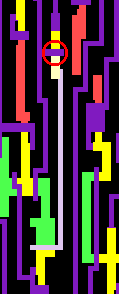

If a wire is "closed off" so that it is no longer connected to neither power nor ground, it will retain its value for a while through capacitance. This is used to store some short-lived data "on the wire" without requiring a latch (this is called dynamic logic, since it has time-dependent behavior beyond just the input clock). As an example, here's the read buffer for the VBL flag, which lets its value be read even though reading $2002 immediately clears the VBL flag:

When the circled gate (/read_2002_output_vblank_flag) goes low, the gate closes, holding the value. When the circled gate is high, the value of vbl_flag (or rather /vbl_flag in this case) is connected to the wire.

Terms

Below are various terms you might run into:

Pull-up transistor: A transistor whose gate when open causes current to flow from a power source. "Pull-up" comes from pulling the wire to a high state.

Pull-up resistor: A resistor connected to power.

Open drain: A type of output that works by sinking current from an external pull-up resistor instead of generating current on its own. An example is the PPU's INT pin. The pull-up resistor is denoted RM1 in this wiring diagram.